2024年3月28日-29日,奇捷科技(Easy-Logic Technology)受邀参加2024国际集成电路展览会暨研讨会(IIC)。在IIC上海同期举办的“EDA与IC设计论坛”上,奇捷科技CEO魏星博士发表了《如何利用增量式设计(ECO)降本增效》的专题演讲,结合实际应用案例分享奇捷科技Function ECO的创新成果及行业干货。

随着数字芯片设计规格日趋复杂、产品迭代周期不断加快,设计过程中难免会出现新的需求、发现新的错误,如何保证项目在出现这些意外的情况下仍然能使整个项目按计划时间完成,已经成为众多芯片设计公司的极大痛点,而这个问题则可以通过增量式设计来解决,业内通常把这种解决方式称之为ECO。

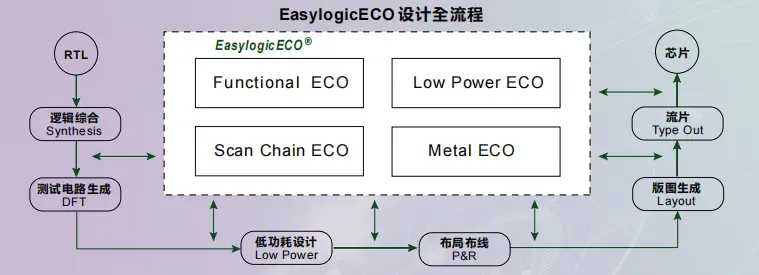

据魏星博士介绍,ECO是一种快速变更ASIC电路功能的设计方法,其通过在当前电路中增加一个很小的补丁逻辑的方法对电路进行逻辑功能变更,从而避免对电路进行完全重新设计。与动辄需要几个月时间的重新设计相比,Function ECO可以确保项目周期,避免项目交付大幅延期从而造成各种不可预估的损失。

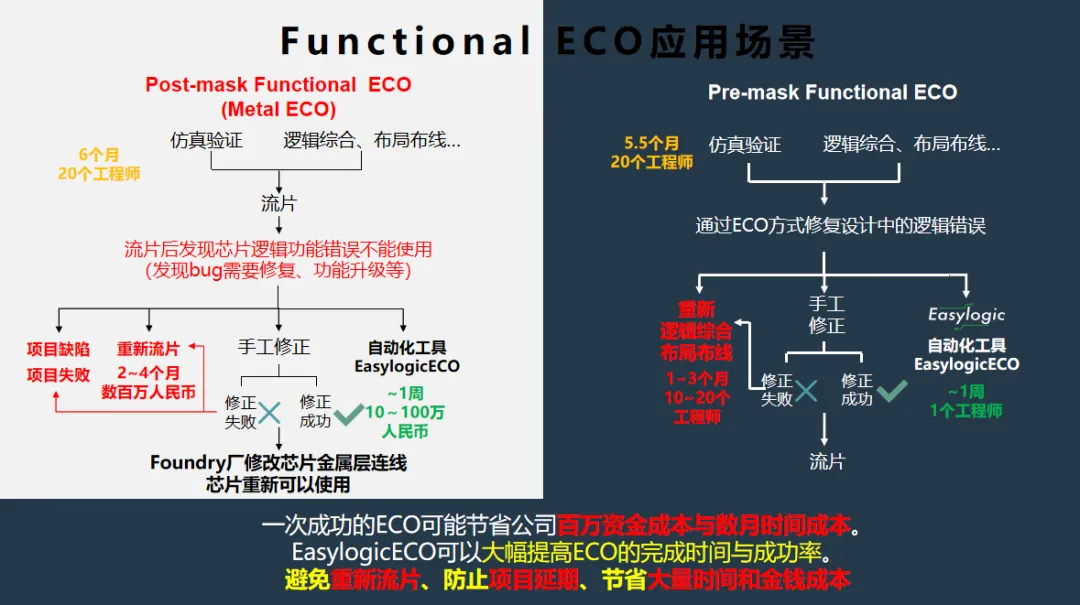

魏星博士介绍,增量式设计流程有两种应用场景:

一种是改版升级场景,流片以后发现芯片逻辑功能错误,比如出现bug需要修复,或者有些新的feature想要添加进去,需要改版升级等情况,传统设计上,我们只能重新设计,这样会大大延长设计周期,增加设计成本,使用增量式设计流程的方法,可能只需要改动几根金属层的连线,从而帮助设计公司节省数月的时间成本及数百万的资金成本;

另外一种是ECO场景,到了项目设计后期,布局布线快要完成,这个时候发现RTL错误或者Spec变更,就需要用到ECO的方式修复设计中的逻辑错误,防止需要重新进行逻辑综合和布局布线等,以保证产品在计划时间内完成。

魏星博士演讲中也列举了一些应用实例,比如在即将Tape-out的设计项目中,发现RTL的变更,乘法器的输入端逻辑需要进行ECO,乘法器被打散,无法在网表中轻易找到Boundary,使用其他工具或者手工ECO生成补丁太大,奇捷科技EasylogicECO解决方案采用独特的逆向工程分析技术,从电路中找出被打散的乘法器边界,配合人工操作,最终只需要增加700逻辑单元,顺利完成时序收敛,帮助设计团队顺利完成项目。

总的来说,通过增量式设计流程,可以有效地保障项目进度,拯救已经流片的错误芯片,并且无需重新流片即可进行升级换代,所以一次成功的ECO,可以帮助企业节省大量的时间及金钱成本。随着其重要性越发凸显,如何搭建一个行之有效的ECO流程也受到越来越多企业的重视,奇捷科技未来也将身体力行,为行业带来相关规范,帮助各芯片设计公司更精准、更有效率地解决IC设计全流程中各个阶段出现的ECO问题,保证项目进度,助力企业降本增效。

此外在展会现场,奇捷科技工作人员与参展嘉宾详细介绍了EasylogicECO产品功能及优势,针对不同的业务需求及挑战进行了深入的探讨,吸引了众多行业内专业人士驻足参观与交流,让参观者更直观地了解奇捷科技Function ECO解决方案及实际应用案例。

此次展会的成功举办,让奇捷科技得以向更多客户展示其可靠且高效的Function ECO解决方案,也期待未来能与各产业同仁有更多的交流,探索更多的合作可能性,共同推动集成电路设计产业的发展和创新。

来源:奇捷科技